## 2A, 30V, 340KHz Synchronous Step-Down Converter

#### DESCRIPTION

The EUP3482A is a synchronous current mode buck regulator capable of driving 2A continuous load current with excellent line and load regulation. The EUP3482A can operate with an input range 4.5V to 30V and the output can be externally set from 0.923V to 12V with a resistor divider.

Fault condition protection includes cycle-by-cycle current limiting and thermal shutdown. In shutdown mode the regulator draws  $1\mu A$  of supply current. Programmable soft-start minimizes the inrush supply current and the output overshoot at initial startup. Automatic pulse skipping mode operation increase efficiency at light loads.

The EUP3482A require a minimum number of external components.

#### **FEATURES**

- 2A Output Current

- Automatic Pulse Skipping Mode at Light Load

- 35V Input Surge Protection

- Integrated  $160 \text{m}\Omega/110 \text{m}\Omega$  DMOS Switches

- 4.5V to 30V Input Operating Range

- Output Adjustable from 0.923V to 12V

- Up to 93% Efficiency

- 1μA Shutdown Current

- Fixed 340KHz Frequency

- Programmable Soft-Start

- Thermal Shutdown and Overcurrent Protection

- Input Supply Overvoltage and Undervoltage Lockout

- 230ns Minimum On Time

- Available in SOP-8 Package

- RoHS Compliant and 100% Lead(Pb)-Free Halogen-Free

#### **APPLICATIONS**

- Distributed Power Systems

- Networking Systems

- PC Monitors

- Portable Electronics

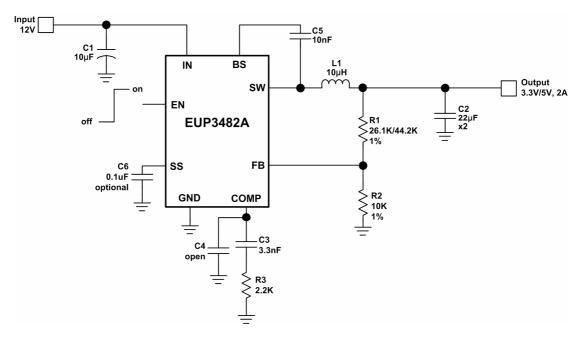

#### **Typical Application Circuit**

Figure 1. 12V to 3.3V/5V Application Circuit

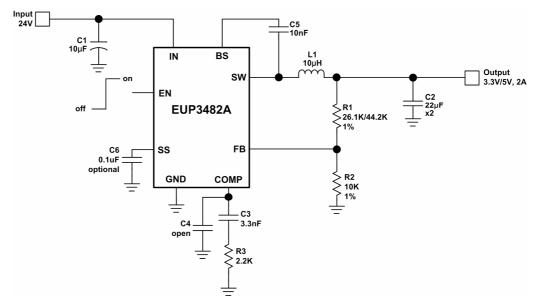

## **Typical Application Circuit (continued)**

Figure 2. 24V to 3.3V/5V application circuit

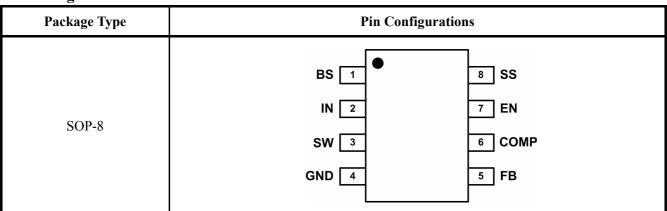

## **Pin Configurations**

## **Pin Description**

| PIN | PIN  | DESCRIPTION                                                                                                                                                                                                                                                                                   |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BS   | High-Side Gate Drive Boost Input. BS supplies the drive for the high-side N-Channel DMOS switch. Connect a 0.01µF or greater capacitor from SW to BS to power the high side switch.                                                                                                           |

| 2   | IN   | Input Supply Pin. IN supplies the power to the IC, as well as the step-down converter switches. Drive IN with a 4.5V to 30V power source. Bypass IN to GND with a suitably large capacitor to minimize input ripple to the IC. See <i>Input Capacitor Section of the applications notes</i> . |

| 3   | SW   | Power Switching Output. Connect the output LC filter from SW to the output load.                                                                                                                                                                                                              |

| 4   | GND  | Ground.                                                                                                                                                                                                                                                                                       |

| 5   | FB   | Output Feedback Input. FB senses the output voltage and regulates it. Drive FB with a resistive voltage divider connected to it from the output voltage. The feedback threshold is 0.923V. See Setting the Output Voltage.                                                                    |

| 6   | COMP | Loop compensation Input. Connect a series RC network from COMP to GND to compensate the regulation control loop. <i>See Compensation</i> .                                                                                                                                                    |

| 7   | EN   | Enable Input. EN is a logic input that controls the regulator on or off. Drive EN high to turn on the regulator; low to turn it off. Don't leave EN pin floating. Directly connect EN to IN (or through a resistance) for automatic startup.                                                  |

| 8   | SS   | Soft-Start Control Input. Connect an external capacitor to program the soft-start. If unused, leave it open, which means internal soft-start function.                                                                                                                                        |

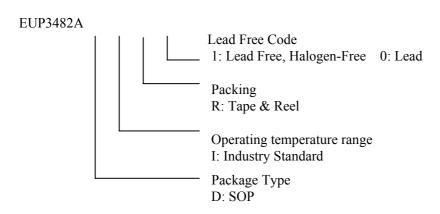

## **Ordering Information**

| Order Number | Package Type | Marking                                | Operating Temperature Range |

|--------------|--------------|----------------------------------------|-----------------------------|

| EUP3482ADIR1 | SOP-8        | ************************************** | -40 °C to +85°C             |

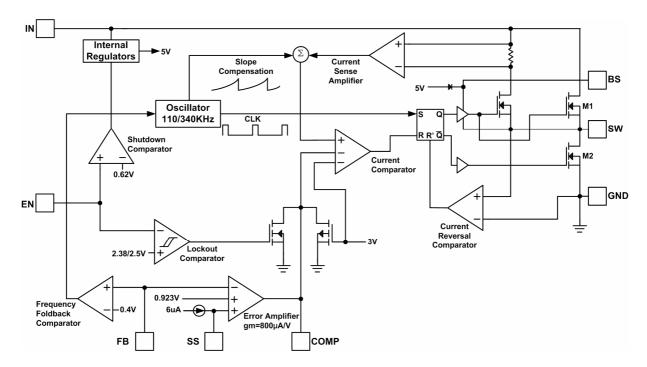

## **Block Diagram**

Figure 3.Functional Block Diagram

## **Absolute Maximum Ratings (1)**

| ■ Supply Voltage (V <sub>IN</sub> )      | 0.3V to +35V                           |

|------------------------------------------|----------------------------------------|

| $\blacksquare$ Enable Voltage $(V_{EN})$ |                                        |

| ■ Switch Voltages (V <sub>SW</sub> )     | 1V to $V_{IN}$ +0.3V                   |

| ■ Boot Voltage (V <sub>BS</sub> )        | $V_{\rm SW}$ -0.3V to $V_{\rm SW}$ +6V |

| ■ All Other Pins                         | -0.3V to +6V                           |

| ■ Junction Temperature                   | 150°C                                  |

| ■ Lead Temperature                       | 260°C                                  |

| ■ Storage Temperature                    |                                        |

| ■ Output Voltage V <sub>OUT</sub>        | 0.923V to 12V                          |

| ■ Thermal Resistance $\theta_{JA}$ (S    | SOP-8) 125°C /W                        |

### **Recommend Operating Conditions (2)**

Input Voltage  $V_{IN}$  ------ 4.5V to 30V

$Note (1): Stress\ beyond\ those\ listed\ under\ "Absolute\ Maximum\ Ratings"\ may\ damage\ the\ device.$

Note(2): The device is not guaranteed to function outside the recommended operating conditions.

### **Electrical Characteristics**

The  $\bullet$  denote specifications which apply over the full operating temperature range, otherwise specification are VIN=12V,  $T_A$ =25°C unless otherwise specified.

| Parameter                              | Conditions                  |   | ]     | Unit  |       |      |  |

|----------------------------------------|-----------------------------|---|-------|-------|-------|------|--|

| rarameter                              | Conditions                  |   | Min.  | Typ.  | Max.  | Unit |  |

| Shutdown Supply Current                | $V_{EN}=0V$                 |   |       | 1     | 5     | μA   |  |

| Supply Current                         | V <sub>FB</sub> =1V         |   |       | 0.45  | 0.9   | mA   |  |

| Feedback Voltage                       | $4.5 \le V_{IN} \le 30V$    |   | 0.905 | 0.923 | 0.941 | V    |  |

| <u> </u>                               |                             | • | 0.895 | 0.923 | 0.951 |      |  |

| Error Amplifier Voltage Gain           |                             |   |       | 360   |       | V/V  |  |

| Error Amplifier Transconductance       | $\Delta I_C = \pm 10 \mu A$ |   |       | 800   |       | μA/V |  |

| High-Side Switch On-Resistance         |                             |   |       | 160   |       | mΩ   |  |

| Low-Side Switch On-Resistance          |                             |   |       | 110   |       | mΩ   |  |

| High-Side Switch Leakage Current       | $V_{EN}=0V$ , $V_{SW}=0V$   |   |       |       | 5     | μΑ   |  |

| Upper Switch Current Limit             | Minimum Duty Cycle          |   | 2.5   | 3.5   |       | A    |  |

| Lower Switch Current Limit             | From Drain to Source        |   |       | 0     |       | A    |  |

| COMP to Current Sense Transconductance |                             |   |       | 7.5   |       | A/V  |  |

| Oscillation Frequency                  |                             |   | 300   | 340   | 380   | KHz  |  |

| Short Circuit Oscillation Frequency    | V <sub>FB</sub> =0V         |   |       | 110   |       | KHz  |  |

| Maximum Duty Cycle                     | V <sub>FB</sub> =0.7V       |   |       | 90    |       | %    |  |

| Minimum On Time                        |                             |   |       | 230   |       | ns   |  |

| EN Disable Threshold                   |                             |   | 0.62  | 1.1   | 1.52  | V    |  |

| EN Disable Threshold                   |                             | • | 0.36  | 1.1   | 1.76  | ]    |  |

| ENII - d4 Thursh -1d                   | V <sub>EN</sub> Rising      |   | 2.3   | 2.5   | 2.8   | V    |  |

| EN Lockout Threshold                   |                             |   | 2     | 2.5   | 3     |      |  |

| EN Lockout Threshold Hysteresis        |                             |   |       | 120   |       | mV   |  |

| Input Under Voltage Lockout Threshold  | V <sub>IN</sub> Falling     |   | 3.8   | 4.1   | 4.4   | V    |  |

| Input Over Voltage Lockout Threshold   | V <sub>IN</sub> Rising      |   |       | 35    |       | V    |  |

| Input Over Voltage Lockout Threshold   |                             |   |       | 2     |       | V    |  |

| Hysteresis                             |                             |   |       |       |       |      |  |

| Soft-Start Charge Current              | V <sub>SS</sub> =0V         |   |       | 6     |       | μA   |  |

| Thermal Shutdown                       |                             |   |       | 160   |       | °C   |  |

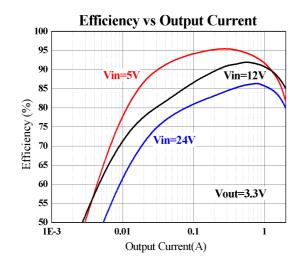

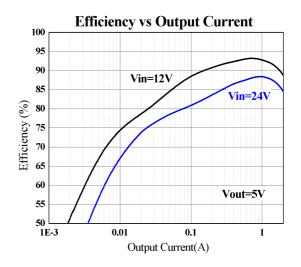

## **Typical Operating Characteristics**

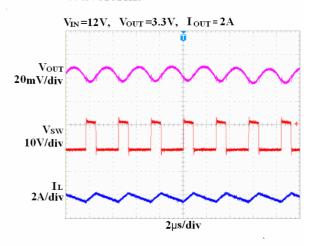

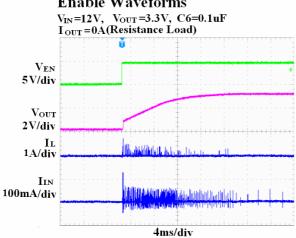

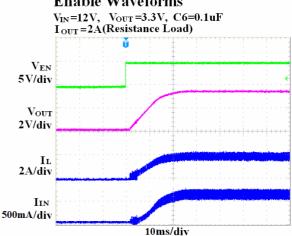

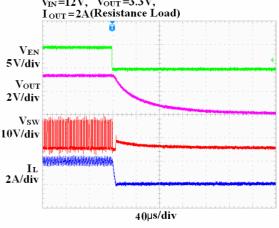

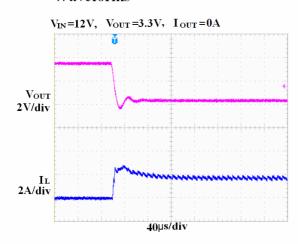

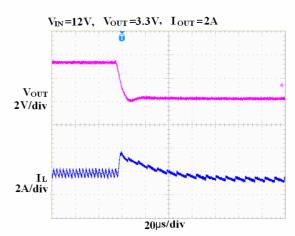

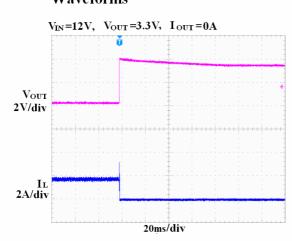

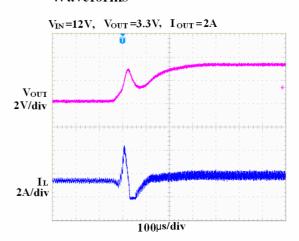

(See Figure 1, C1=10 $\mu$ F, C2=22 $\mu$ F × 2, L=10 $\mu$ H, T<sub>A</sub>=+25°C)

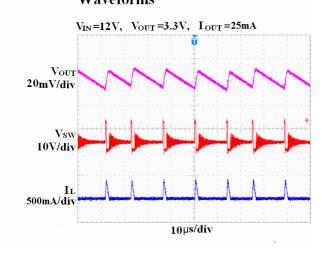

## Steady State Test Waveforms

## Steady State Test Waveforms

## External Startup through Enable Waveforms

## External Startup through Enable Waveforms

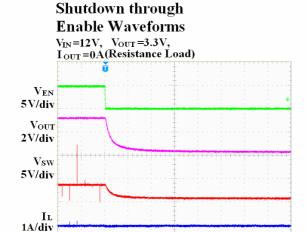

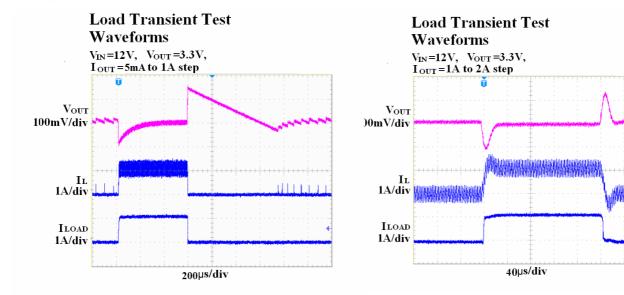

## **Typical Operating Characteristics (continued)**

(See Figure 1, C1=10 $\mu$ F, C2=22 $\mu$ F × 2, L=10 $\mu$ H, T<sub>A</sub>=+25°C)

10ms/div

#### Shutdown through Enable Waveforms V<sub>IN</sub>=12V, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=2A(Resistance Load)

## Short Circuit Test Waveforms

## Short Circuit Test Waveforms

# Short Circuit Recovery Waveforms

## Short Circuit Recovery Waveforms

# Typical Operating Characteristics (continued) (See Figure 1, C1=10μF, C2=22μF × 2, L=10μH, T<sub>A</sub>=+25°C)

## **Functional Description**

The EUP3482A regulates input voltages from 4.5V to 30V down to an output voltage as low as 0.923V, and supplies up to 2A of load current.

The EUP3482A uses current-mode control to regulate the output voltage. The output voltage is measured at FB through a resistive voltage divider and amplified through the internal transconductance error amplifier. The voltage at the COMP pin is compared to the switch current (measured internally) to control the output voltage.

The converter uses internal N-Channel MOSFET switches to step-down the input voltage to the regulated output voltage. Since the high side MOSFET requires a gate voltage greater than the input voltage, a boost capacitor connected between SW and BS is needed to drive the high side gate. The boost capacitor is charged from the internal 5V rail when SW is low.

At light loads, the inductor current may reach zero or reverse on each pulse. The bottom DMOS is turned off by the current reversal comparator and the switch voltage will ring. This is discontinuous mode operation, and is normal behavior for the switching regulator. At light load, the EUP3482A will automatically skip pulses in pulse skipping mode operation to maintain output regulation and increases efficiency.

When the FB pin voltage exceeds 15% of the nominal regulation value of 0.923V, the over voltage comparator is tripped and forcing the high-side switch off

#### **Application Information**

#### **Setting the Output Voltage**

The output voltage is set using a resistive voltage divider connected from the output voltage to FB. The voltage divider divides the output voltage down to the feedback voltage by the ratio:

$$V_{FB} = V_{OUT} \frac{R2}{R1 + R2}$$

Thus the output voltage is:

$$V_{OUT} = 0.923 * \frac{R1 + R2}{R2}$$

R2 can be as high as  $100k\Omega$ , but a typical value is  $10k\Omega$ . Using the typical value for R2, R1 is determined by:

$$R1 = 10.83 * (V_{OLIT} - 0.923) (k\Omega)$$

For example, for a 3.3V output voltage, R2 is  $10k\Omega$  and R1 is  $26.1k\Omega$ .

#### **Inductor**

The inductor is required to supply constant current to the load while being driven by the switched input voltage. A larger value inductor will result in less ripple current that will in turn result in lower output ripple voltage. However, the larger value inductor will have a larger physical size, higher series resistance, and/or lower saturation current. A good rule for determining inductance is to allow the peak-to-peak ripple current to be approximately 30% of the maximum switch current limit. Also, make sure that the peak inductor current is below the maximum switch current limit.

The inductance value can be calculated by:

$$L = \frac{V_{OUT}}{f_{S} * \Delta I_{L}} * \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Where  $V_{OUT}$  is the output voltage,  $V_{IN}$  is the input voltage,  $f_S$  is the switching frequency, and  $\Delta I_L$  is the peak-to-peak inductor ripple current.

Choose an inductor that will not saturate under the maximum inductor peak current, calculated by:

$$I_{LP} = I_{LOAD} + \frac{V_{OUT}}{2 * f_{S} * L} * \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Where I<sub>LOAD</sub> is the load current.

The choice of which style inductor to use mainly depends on the price vs. size requirements and any EMI constraints.

#### **Optional Schottky Diode**

During the transition between the high-side switch and low-side switch, the body diode of the low-side power MOSFET conducts the inductor current. The forward voltage of this body diode may be high and cause efficiency loss. An optional small 1A Schottky diode B130 in parallel with low-side switch is recommended to improve overall efficiency when input voltage is higher.

#### **Input Capacitor**

The input current to the step-down converter is discontinuous, therefore a capacitor is required to supply the AC current while maintaining the DC input voltage. Use low ESR capacitors for the best performance. Ceramic capacitors are preferred, but tantalum or low-ESR electrolytic capacitors will also suffice. Choose X5R or X7R dielectrics when using ceramic capacitors.

Since the input capacitor (C1) absorbs the input switching current, it requires an adequate ripple current rating. The RMS current in the input capacitor can be estimated by:

$$I_{C1} = I_{LOAD} * \sqrt{\frac{V_{OUT}}{V_{IN}}} * \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

The worst-case condition occurs at  $V_{\rm IN} = 2V_{\rm OUT}$ , where  $I_{\rm C1} = I_{\rm LOAD}/2$ . For simplification, use an input capacitor with a RMS current rating greater than half of the maximum load current.

The input capacitor can be electrolytic, tantalum or ceramic. When using electrolytic or tantalum capacitors, a small, high quality ceramic capacitor, i.e.  $0.1\mu F$ , should be placed as close to the IC as possible. When using ceramic capacitors, make sure that they have enough capacitance to provide sufficient charge to prevent excessive voltage ripple at input. The input voltage ripple for low ESR capacitors can be estimated by:

$$\Delta V_{IN} = \frac{I_{LOAD}}{C1 * f_{S}} * \frac{V_{OUT}}{V_{IN}} * \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Where C1 is the input capacitance value.

For simplification, choose the input capacitor whose RMS current rating greater than half of the maximum load current.

### **Output Capacitor**

The output capacitor (C2) is required to maintain the DC output voltage. Ceramic, tantalum, or low ESR electrolytic capacitors are recommended. Low ESR capacitors are preferred to keep the output voltage ripple low. The output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_{S} * L} * \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

$$* \left( R_{ESR} + \frac{1}{8 * f_{S} * C2} \right)$$

Where C2 is the output capacitance value and  $R_{\rm ESR}$  is the equivalent series resistance (ESR) value of the output capacitor.

When using ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance which is the main cause for the output voltage ripple. For simplification, the output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 * f_S^2 * L * C2} * \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

When using tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated to:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_{S} * L} * \left(1 - \frac{V_{OUT}}{V_{IN}}\right) * R_{ESR}$$

The characteristics of the output capacitor also affect the stability of the regulation system. The EUP3482A can be optimized for a wide range of capacitance and ESR values.

#### **Compensation Components**

EUP3482A employs current mode control for easy compensation and fast transient response. The system stability and transient response are controlled through the COMP pin. COMP is the output of the internal transconductance error amplifier. A series capacitor-resistor combination sets a pole-zero combination to govern the characteristics of the control system.

The DC gain of the voltage feedback loop is given by:

$$A_{VDC} = R_{LOAD} *G_{CS} *A_{VEA} *\frac{V_{FB}}{V_{OUT}}$$

Where  $V_{FB}$  is the feedback voltage (0.923V),  $A_{VEA}$  is the error amplifier voltage gain,  $G_{CS}$  is the current sense transconductance and  $R_{LOAD}$  is the load resistor value.

The system has two poles of importance. One is due to the compensation capacitor (C3) and the output resistor of the error amplifier, and the other is due to the output capacitor and the load resistor. These poles are located at:

$$f_{P1} = \frac{G_{EA}}{2\pi * C3 * A_{VEA}}$$

$$f_{P2} = \frac{1}{2\pi * C2 * R_{LOAD}}$$

Where  $G_{EA}$  is the error amplifier transconductance.

The system has one zero of importance, due to the compensation capacitor (C3) and the compensation resistor (R3). This zero is located at:

$$f_{Z1} = \frac{1}{2\pi * C3 * R3}$$

The system may have another zero of importance, if the output capacitor has a large capacitance and/or a high ESR value. The zero, due to the ESR and capacitance of the output capacitor, is located at:

$$f_{ESR} = \frac{1}{2\pi * C2 * R_{ESR}}$$

In this case, a third pole set by the compensation capacitor (C4) and the compensation resistor (R3) is used to compensate the effect of the ESR zero on the loop gain. This pole is located at:

$$f_{P3} = \frac{1}{2\pi * C4 * R3}$$

The goal of compensation design is to shape the converter transfer function to get a desired loop gain. The system crossover frequency where the feedback

loop has the unity gain is important. Lower crossover frequencies result in slower line and load transient responses, while higher crossover frequencies could cause the system instability. A good standard is to set the crossover frequency below one-tenth of the switching frequency.

To optimize the compensation components, the following procedure can be used:

1. Choose the compensation resistor (R3) to set the desired crossover frequency.

Determine R3 by the following equation:

$$R3 = \frac{2\pi * C2 * f_{C}}{G_{EA} * G_{CS}} * \frac{V_{OUT}}{V_{FB}}$$

$$< \frac{2\pi * C2 * 0.1 * f_{S}}{G_{EA} * G_{CS}} * \frac{V_{OUT}}{V_{FB}}$$

Where  $f_C$  is the desired crossover frequency, which is typically below one tenth of the switching frequency.

2. Choose the compensation capacitor (C3) to achieve the desired phase margin. For applications with typical inductor values, setting the compensation zero  $(f_{Z1})$  below one-forth of the crossover frequency provides sufficient phase margin.

Determine C3 by the following equation:

$$C3 > \frac{4}{2\pi * R3 * f_C}$$

Where R3 is the compensation resistor.

3. Determine if the second compensation capacitor (C4) is required. It is required if the ESR zero of the output capacitor is located at less than half of the switching frequency, or the following relationship is valid:

$$\frac{1}{2\pi * C2 * R} < \frac{f_S}{2}$$

If this is the case, then add the second compensation capacitor (C4) to set the pole  $f_{P3}$  at the location of the ESR zero. Determine C4 by the equation:

$$C4 = \frac{C2 * R}{R3}$$

To simplify design efforts using the EUP3482A, the typical design for common application are listed in Table1.

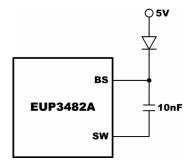

#### **External Bootstrap Diode**

It is recommended that an external bootstrap diode be added when the system has a 5V fixed input or the power supply generates a 5V output. This helps improve the efficiency of the regulator.

Figure 4. Add Optional External Bootstrap Diode to Enhance

This diode is also recommended for high duty cycle operation ( when  $\frac{V_{OUT}}{V_{IN}}$  >65% ) and high output voltage ( $V_{OUT}$  >12V) applications.

| Table1. External Comp | onents for Ty | ypical Designs |

|-----------------------|---------------|----------------|

|-----------------------|---------------|----------------|

| Vin(V) | Vout(V) | L1(uH) | C2(uF) | R1(KΩ) | R2(KΩ) | R3(KΩ) | C3(nF) | C4(pF) |

|--------|---------|--------|--------|--------|--------|--------|--------|--------|

| 5      | 1.0     | 3.3    | 22*2   | 0.845  | 10     | 2.2    | 3.3    | open   |

| 5      | 1.2     | 4.7    | 22*2   | 3.0    | 10     | 2.2    | 3.3    | open   |

| 5      | 3.3     | 10     | 22*2   | 26.1   | 10     | 2.2    | 3.3    | open   |

| 12     | 1.0     | 3.3    | 22*2   | 0.845  | 10     | 2.2    | 10     | open   |

| 12     | 1.2     | 4.7    | 22*2   | 3.0    | 10     | 2.2    | 10     | open   |

| 12     | 3.3     | 10     | 22*2   | 26.1   | 10     | 2.2    | 3.3    | open   |

| 12     | 5.0     | 10     | 22*2   | 44.2   | 10     | 2.2    | 3.3    | open   |

| 24     | 3.3     | 10     | 22*2   | 26.1   | 10     | 2.2    | 3.3    | open   |

| 24     | 5.0     | 10     | 22*2   | 44.2   | 10     | 2.2    | 3.3    | open   |

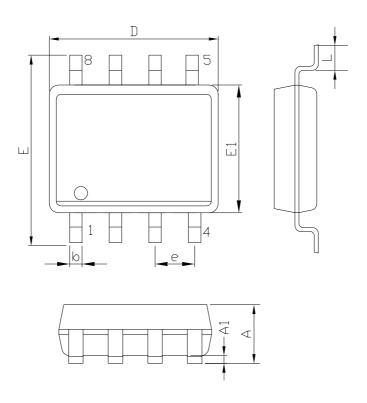

## **Packaging Information**

SOP-8

| SYMBOLS | MILLIM | ETERS | INCHES      |       |  |

|---------|--------|-------|-------------|-------|--|

|         | MIN.   | MAX.  | MIN.        | MAX.  |  |

| A       | 1.35   | 1.75  | 0.053 0.0   |       |  |

| A1      | 0.10   | 0.25  | 0.004       | 0.010 |  |

| D       | 4.9    | 90    | 0.193       |       |  |

| Е       | 5.80   | 6.20  | 0.228       | 0.244 |  |

| E1      | 3.90   |       | 0.153       |       |  |

| L       | 0.40   | 1.27  | 0.016       | 0.050 |  |

| b       | 0.31   | 0.51  | 0.012 0.020 |       |  |

| e       | 1.27   |       | 0.0         | 050   |  |